Remember magnetic core memory? Maybe you don’t, if you weren’t around in the ’50s or ’60s (or aren’t a tech junkie like me). But it was one of the key developments during the evolution of the modern computer. At a time when large scale integration on silicon was just beginning and massive silicon memories were infeasible, core memory fulfilled a critical need for larger, faster memories for some of the early big-iron mainframes.

Core memory is interesting because it’s one of the simpler memory constructs to understand, even today. The basis of the system is a humble ferrite ring (a “core”). The core material is formulated to exhibit high magnetic remanence – that is, it retains a magnetic field very well. By utilizing Ampère’s law and passing a pulse of current through a wire threaded through the center of the core, a persistent magnetic field can be induced. Applying Faraday’s Law, it is then possible to “read out” the state of the core – if the core already has had a field induced within it, then passing another current pulse has no effect; otherwise, a slight voltage pulse is developed across any wires passing through it,, which can be measured.

Expanding the scope a bit, it is possible to write to and read from a large quantity of cores if they are arranged on a two-dimensional grid. As a result of the particular magnetic properties of the cores, they only change state when a sufficiently large current is passed through them. This current can be split to any arbitrary number of wires; as long as the sum of the currents is above the minimum for the material, the field is induced. If we pass half the necessary current through one row of a two-dimensional array of cores, and half the necessary current through one column of the same array, we can affect only one chosen core in the array. An additional wire passing through all cores is typically used to detect the state of the chosen core.

I have an ambitious design in mind which will get a more detailed post later, but suffice it to say for now that I’m planning a combination art and engineering project which needs a bank of memory. I could go the simple route and put a simple DIP SRAM in, but that’s no fun to look at. But I bought a little can of 50,000 memory cores a few years ago, and that seems like it might be a little more fun. That’s enough for a 4KB array, which ought to be enough for what I’m planning. But before I spend several weeks building a 32,000 core array, it’s important to understand how the assembly will work. To that end, I’ve planned a few baby-steps to build up to the real deal.

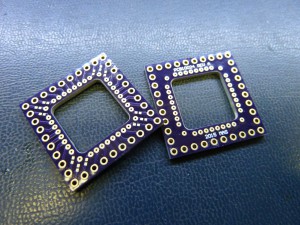

I’ve designed a simple PCB with a large route-out in the center and an array of holes around the outside. The board is designed as a carrier for a small 8×8 array of cores and their associated wiring. Because my application calls for byte-addressable memory, the eventual plan is to stack eight such boards to support parallel access of an entire byte, but at this point testing will begin with a single 64-bit array.

The corner pads are isolated by 0402 0-ohm jumpers for flexibility in stacking and addressing boards.

A core memory build is more like sewing than it is electrical assembly. Very thin thread-like wire is woven through the cores, and the end product resembles cloth. At the height of core memory usage there were many factories of very skilled workers who wove these memories day in and day out. In the process of building my tiny memory, I quickly found that there are assembly methods that work very well, but there are also methods that end up in immediate frustration. You quickly get into a groove, so while the first rows take a while, by the end the focus sets in and hours can pass in an instant as the board comes together.

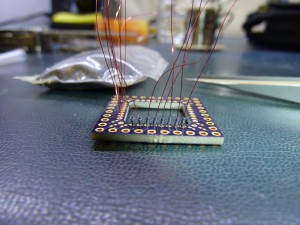

Speaking of first rows, let’s begin! First, we solder some stubs of 36AWG enamel wire to the board along two adjacent edges, then thread eight teeny-tiny cores onto each of the eight wires on one side of the board:

Now the wires are threaded through the pads on the other side of the board and pulled taut, then soldered into place, thereby trapping the cores:

Now the wires are threaded through the pads on the other side of the board and pulled taut, then soldered into place, thereby trapping the cores:

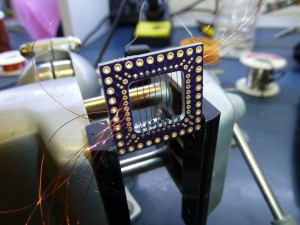

Before we continue, an explanation is necessary. There are a number of different ways to orient the cores. They can all be mounted parallel to each other, they can alternate by rows, they can alternate at every part. I chose to alternate at every part – this can reduce magnetic coupling between adjacent cores, and can enable the use of simpler read/write hardware. It also looks pretty neat. So after a while, the array looks like this:

Before we continue, an explanation is necessary. There are a number of different ways to orient the cores. They can all be mounted parallel to each other, they can alternate by rows, they can alternate at every part. I chose to alternate at every part – this can reduce magnetic coupling between adjacent cores, and can enable the use of simpler read/write hardware. It also looks pretty neat. So after a while, the array looks like this:

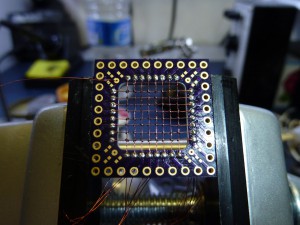

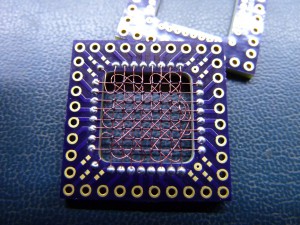

Now that the main array wires are all installed, the sense wire must be threaded through all the cores. Each core must have the sense wire passed through it exactly once. With the cores in this arrangement, this is simplest to accomplish by passing the wires through the cores diagonally, first in one direction, then the other. That leaves us with an end product that looks something like this:

Now that the main array wires are all installed, the sense wire must be threaded through all the cores. Each core must have the sense wire passed through it exactly once. With the cores in this arrangement, this is simplest to accomplish by passing the wires through the cores diagonally, first in one direction, then the other. That leaves us with an end product that looks something like this:

And that’s the current state of things. The corner jumpers and connectors still need to be installed, but that will come when the interface hardware has been developed. There’s still plenty of work to do, so watch for followup post(s) later on.

And that’s the current state of things. The corner jumpers and connectors still need to be installed, but that will come when the interface hardware has been developed. There’s still plenty of work to do, so watch for followup post(s) later on.

Schematics and Gerbers for this board will be posted… as soon as I get around to it. below:

PCB10024 REV A GERBERS (zip, 6KB)

SCH10024 REV A (pdf, 18KB)

Please note: The board has a large cut-out in the center. The first time I ordered these, OSH Park correctly routed to the edge of the definition line (as shown in the above photos). The second time, they routed on the center of the definition line, cutting into the ring of pads. The resulting boards are functional, just not as pretty. Watch out for that.

Dean sir,

Are these PCB available for sale ?

I would buy some pièces for sure.

Please let me Know

Best regards,

Fred from France

Thanks for this nice post.

Where can i buy these little cards ?

Best regards,

Fred from france

I’ve (finally) posted the board documents so you can order some from your favorite PCB fab if you’d like 🙂

I won’t be selling boards or assemblies, unfortunately… trust me, there’s no price you’d be willing to pay that would make it worthwhile to build one of these things for you, they’re extremely tedious… from the first photo above to the last, more than six hours elapsed!